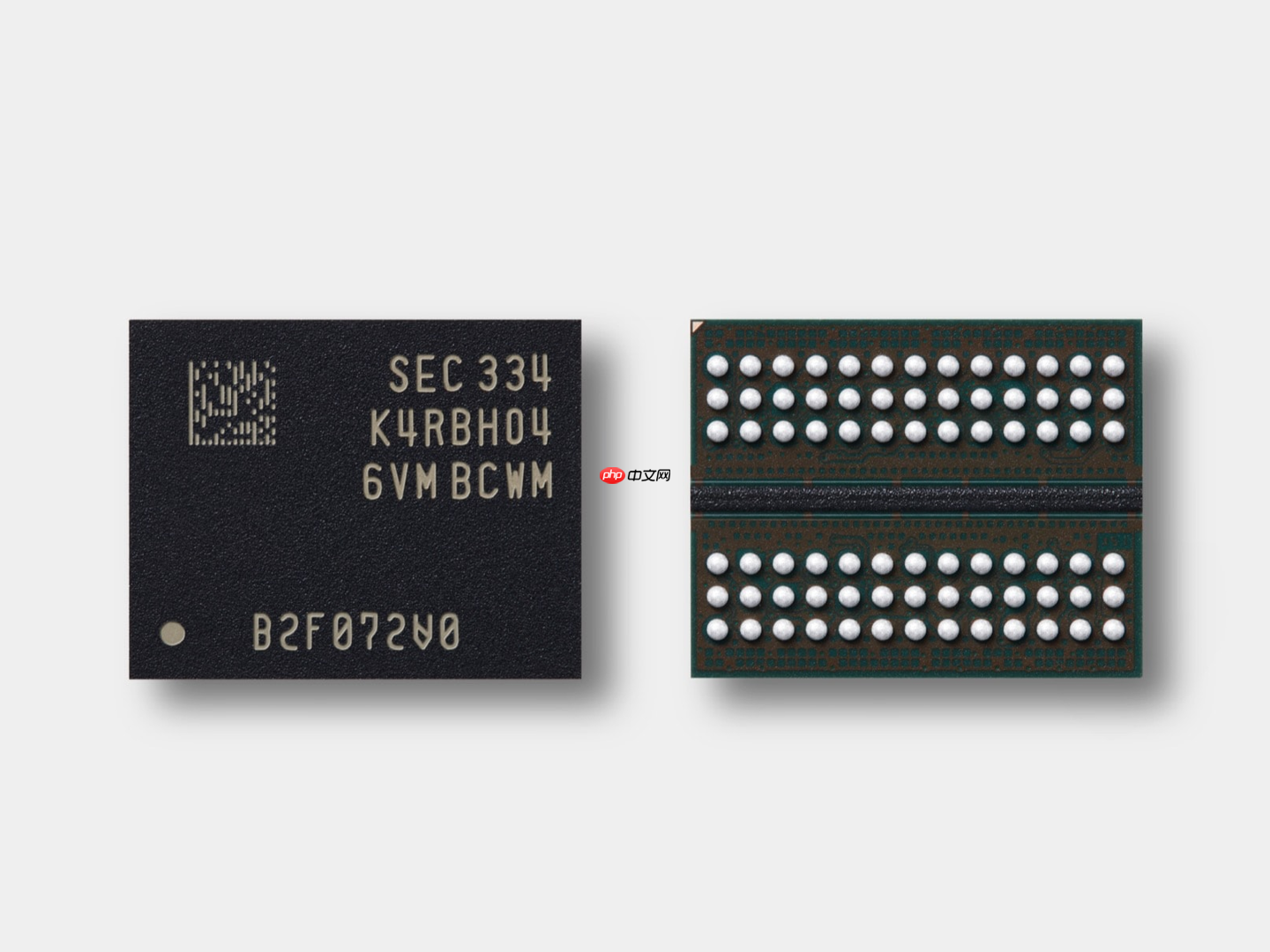

三星电子1c纳米DRAM内存良率大幅提升,设计改进成关键因素

据最新消息,三星电子在 1c 纳米 DRAM 内存技术方面取得了显著进展,据悉,该公司通过设计改进成功提升了内存良率,这将有助于提高其内存产品的生产效率及市场竞争力,这一突破对于整个半导体行业来说具有重要意义,有望推动相关技术的进一步发展和创新,摘要字数控制在 100-200字以内。

6 月 24 日消息,据韩国媒体 sedaily 当地时间本月 19 日的报道以及另一家韩媒 mk 今日的报道,三星电子第六代 10 纳米级(注:即 1c nm)dram 内存制造工艺,在设计优化等因素推动下,良率实现了显著提升。

SEDaily 报道指出,三星去年在 1c nm 内存上的良率尚不足 30%,而今年五月份进行的性能测试中,良率已上升至 50%~70%;MK 则提到了近期良率已超过 60% 的数据。

两家媒体均表示,此次良率大幅提升主要得益于重大的设计调整,尽管这种改动可能会导致量产时间有所推迟,但在技术上取得了明显的进步。

由于在 HBM 市场上的失利,三星电子在今年第一季度将 DRAM 内存营收冠军的位置让给了 SK 海力士。考虑到三星即将推出的 HBM4 内存正是基于 1c nm 工艺,该技术良率的改善有望为三星的重新崛起提供有力支撑。

下一篇 >>

网友留言(0 条)