台积电挑战CoWoS封装极限,突破技术壁垒,实现大尺寸光罩与高效能HBM4堆叠技术(预计于2027年实现)

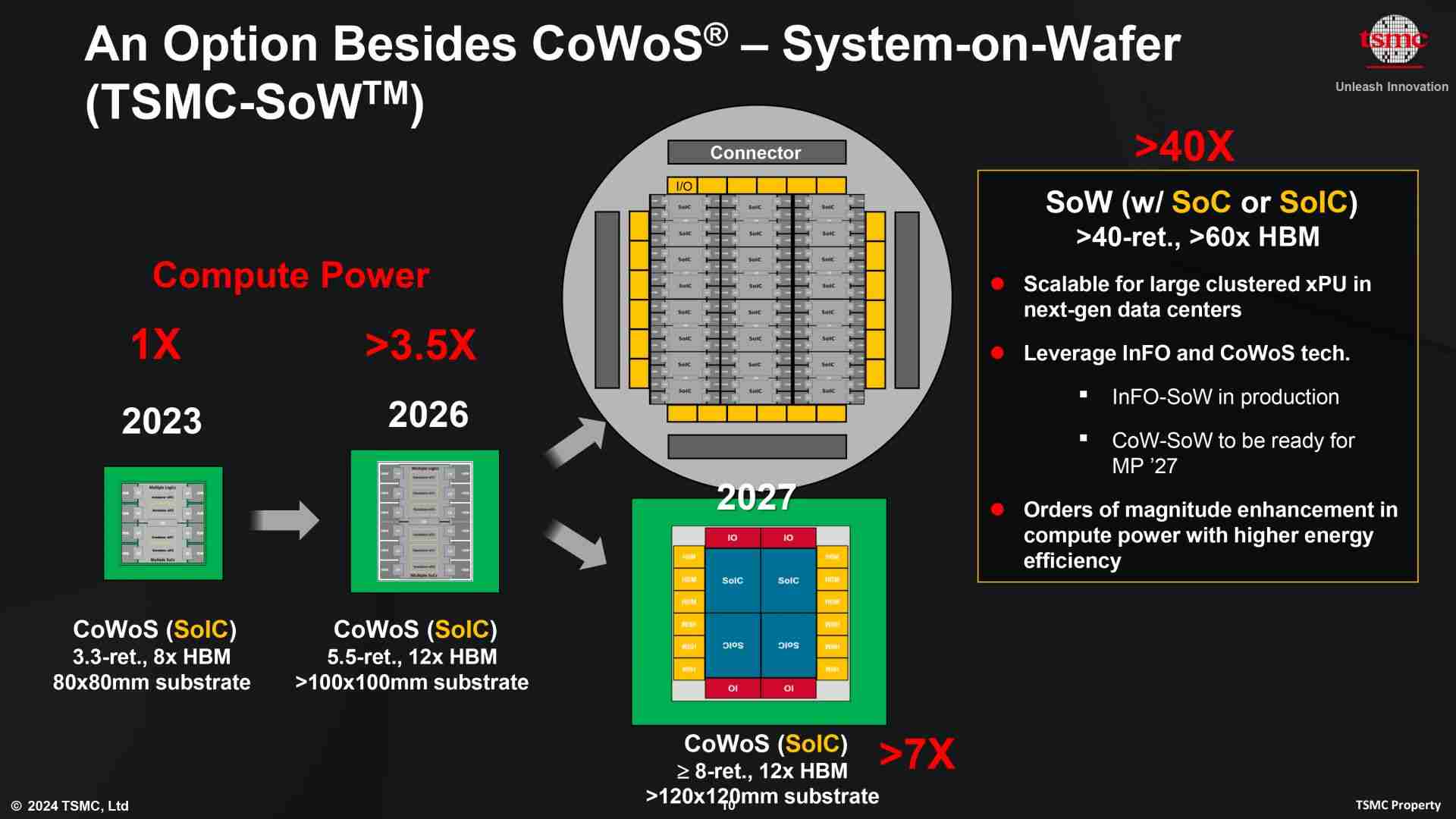

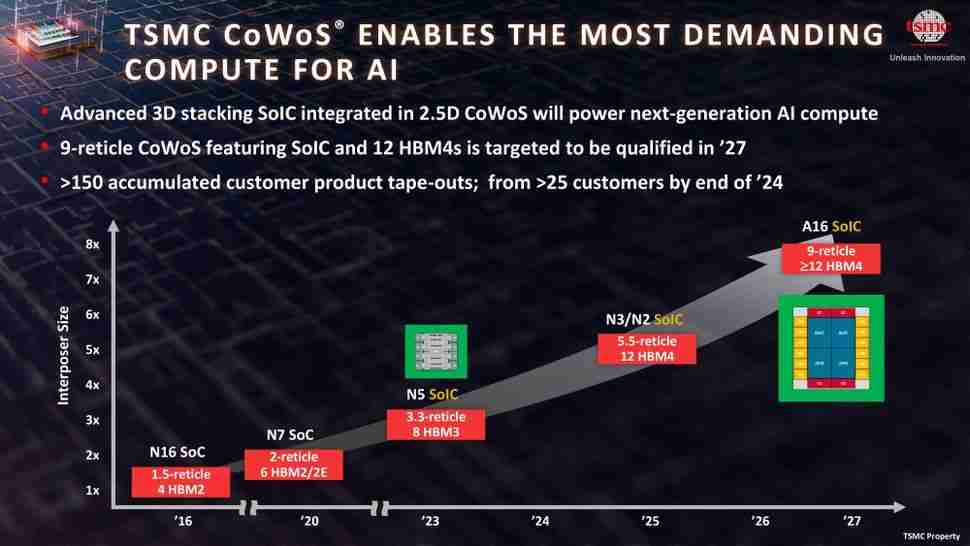

台积电正挑战CoWoS封装技术的极限,计划于2027年实现大幅超越现有技术水平的突破,届时,其光罩尺寸将达到惊人的9倍增长,面积达7722平方毫米,该公司还将实现12个HBM4堆叠技术,这将极大提升存储密度和性能,这一创新将推动半导体行业迈向新的里程碑,为未来的计算和存储应用提供强大的技术支持。

本站 11 月 29 日消息,在本月召开的欧洲开放创新平台(oip)论坛上,台积电宣布计划在 2027 年推出超大尺寸版晶圆级封装(cowos)技术,最高实现 9 倍光罩尺寸(reticle sizes)和 12 个 hbm4 内存堆叠。

台积电每年都会推出新的工艺技术,尽最大努力满足客户对功耗、性能和面积(PPA)改进的需求。对于有更高性能需求的客户来说,EUV 光刻工具现有的光罩尺寸(858 平方毫米)是不够的。

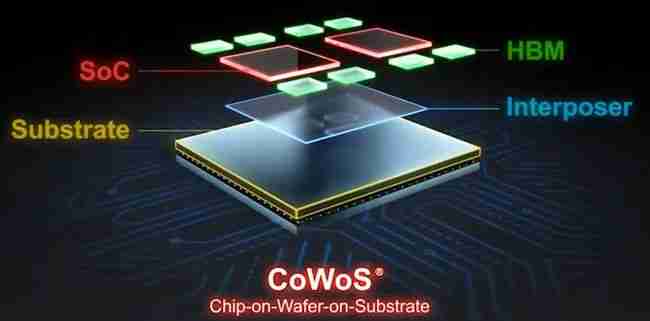

本站注:台积电于 2016 年推出的初代 CoWoS 封装方案,支持大约 1.5 倍光罩尺寸,而目前已经提升到 3.3 倍,可以封装 8 个 HBM3 堆栈。

台积电承诺在 2025~2026 年期间,支持 5.5 倍光罩尺寸,和最高 12 个 HBM4 内存堆叠;并计划在 2027 年推出“Super Carrier” 9 倍光罩尺寸的 CoWoS 封装方案,为芯粒(chiplets)和内存提供高达 7722 平方毫米的空间。

网友留言(0 条)